中清航科WLCSP测试一体化方案缩短生产周期。集成探针卡与临时键合层,实现300mm晶圆单次测试成本降低40%。在PMIC量产中,测试覆盖率达99.2%。面向航天应用,中清航科抗辐照封装通过MIL-STD-750认证。掺铪二氧化硅钝化层使总剂量耐受>300krad,单粒子翻转率<1E-10error/bit-day。已服务低轨卫星星座项目。中清航科MEMS真空封装良率突破98%。采用多孔硅密封技术,腔体真空度维持<0.1Pa十年以上。陀螺仪零偏稳定性达0.5°/h,满足导航级应用。存储芯片封装求快求稳,中清航科接口优化,提升数据读写速度与稳定性。表贴封装

中清航科MIL-STD-883认证产线实现金锡共晶焊接工艺。在宇航级FPGA封装中,气密封装漏率<5×10⁻⁸atm·cc/s,耐辐照总剂量达100krad。三防涂层通过96小时盐雾试验,服务12个卫星型号项目。中清航科推出玻璃基板中介层技术,介电常数低至5.2@10GHz。通过TGV玻璃通孔实现光子芯片与电芯片混合集成,耦合损耗<1dB。该平台已用于CPO共封装光学引擎开发,传输功耗降低45%。中清航科建立全维度失效分析实验室。通过3DX-Ray实时监测BGA焊点裂纹,结合声扫显微镜定位分层缺陷。其加速寿命测试模型可精确预测封装产品在高温高湿(85℃/85%RH)条件下的10年失效率。上海半导体封装 基板车规芯片封装求稳,中清航科全生命周期测试,确保十年以上可靠运行。

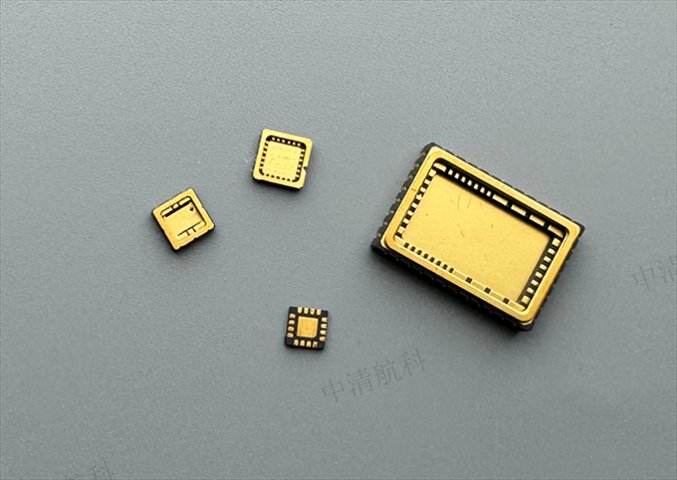

先进芯片封装技术-晶圆级封装(WLP):晶圆级封装是在晶圆上进行封装工艺,实现了芯片尺寸与封装尺寸的接近,减小了封装体积,提高了封装密度。与传统先切割晶圆再封装不同,它是先封装后切割晶圆。中清航科的晶圆级封装技术处于行业前沿,能够为客户提供高集成度、小型化的芯片封装产品,在物联网、可穿戴设备等对芯片尺寸和功耗要求苛刻的领域具有广阔应用前景。想要了解更多内容可以关注我司官网,另外有相关需求欢迎随时联系。

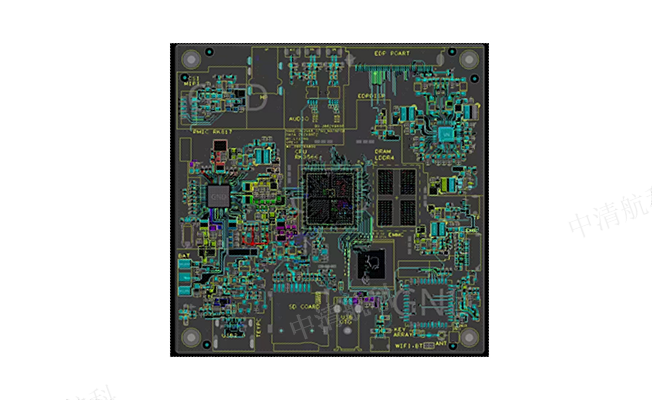

先进芯片封装技术-系统级封装(SiP):SiP是将多个不同功能的芯片以并排或叠加的方式,封装在一个单一的封装体内,实现系统级的功能集成。与SoC(系统级芯片)相比,SiP无需复杂的IP授权,设计更灵活、成本更低。中清航科在SiP技术上积累了丰富经验,能够根据客户需求,将多种芯片高效整合在一个封装内,为客户提供具有成本优势的系统级封装解决方案,广泛应用于消费电子、汽车电子等领域。想要了解更多详细内容可以关注我司官网。航空芯片环境严苛,中清航科封装方案,耐受高低温与强辐射考验。

芯片封装的标准化与定制化平衡:芯片封装既有标准化的产品以满足通用需求,也有定制化的服务以适应特殊场景。如何平衡标准化与定制化,是企业提升竞争力的关键。中清航科拥有丰富的标准化封装产品系列,能快速满足客户的通用需求;同时,公司具备强大的定制化能力,可根据客户的特殊要求,从封装结构、材料选择到工艺设计,提供多方位的定制服务,实现标准化与定制化的灵活平衡。想要了解更多内容可以关注我司官网,同时欢迎新老客户来电咨询。医疗芯片求稳求精,中清航科封装方案,满足高可靠性与生物兼容性。半导体封装测试厂

中清航科芯片封装方案,适配车规级严苛要求,助力汽车电子安全升级。表贴封装

芯片封装的散热设计:随着芯片集成度不断提高,功耗随之增加,散热问题愈发突出。良好的散热设计能确保芯片在正常温度范围内运行,避免因过热导致性能下降甚至损坏。中清航科在芯片封装过程中,高度重视散热设计,通过优化封装结构、选用高导热材料、增加散热鳍片等方式,有效提升封装产品的散热性能。针对高功耗芯片,公司还会采用先进的液冷散热封装技术,为客户解决散热难题,保障芯片长期稳定运行,尤其在数据中心、高性能计算等领域发挥重要作用。表贴封装