FPGA开发板在能源管理系统中的应用有助于提高能源利用效率。在智能电网领域,开发板可通过连接各类电力传感器,实时采集电网中的电压、电流、功率等参数。对采集到的数据进行分析处理,监测电网的运行状态,判断电网是否处于正常工作范围。当检测到电网出现异常情况,如电压波动过大、功率失衡等,开发板可及时发出预警信息,并将数据上传至电网管理中心,为管理人员进行决策提供依据。在可再生能源发电系统中,如太阳能发电、风力发电等,开发板可用于发电设备的运行。根据环境条件,如光照强度、风速等,调节发电设备的工作参数,实现最大功率点,提高能源转换效率。同时,开发板还可以对发电系统的电能质量进行监测与优化,确保发电系统稳定可靠地向电网供电,促进能源行业的可持续发展。FPGA 开发板电源模块保障稳定供电输出。江苏ZYNQFPGA开发板学习板

FPGA开发板的离线运行是指不依赖计算机,通过外部存储设备(如SPIFlash、SD卡)加载配置文件和应用程序,适合嵌入式系统和现场应用场景。离线运行设计需满足两个**需求:一是配置文件的自动加载,二是应用程序执行。配置文件自动加载可通过FPGA的上电配置功能实现,将编译后的.bit文件存储到SPIFlash中,FPGA上电后自动从Flash读取配置文件,完成初始化;部分开发板支持多配置文件存储,可通过板载按键或外部信号选择加载的配置文件。应用程序**执行需FPGA实现完整的功能逻辑,包括外设控制、数据处理和交互功能,例如设计一个离线数据采集系统,FPGA从传感器采集数据,存储到SD卡,通过LED显示工作状态,无需计算机干预。离线运行还需考虑系统稳定性,例如加入watchdog(看门狗)电路,当系统出现死机时自动重启;加入电源管理模块,支持低功耗模式,延长电池供电时间。 四川开发FPGA开发板核心板FPGA 开发板示例代码提供设计模板参考。

科研人员在进行前沿技术研究时,FPGA开发板是重要的工具之一。在人工智能领域,科研人员利用开发板实现神经网络算法的硬件加速,通过编程优化神经网络计算过程,提高计算效率。在生物医学工程(不涉及医疗内容)领域外的相关研究中,如生物传感器信号处理研究,开发板可用于处理生物电信号,分析信号特征。FPGA开发板的灵活性与可编程性,使科研人员能够快速实现新的研究思路与算法,对采集的数据进行实时处理与分析,为各领域前沿技术研究提供实验平台,推动科研工作的进展与创新。

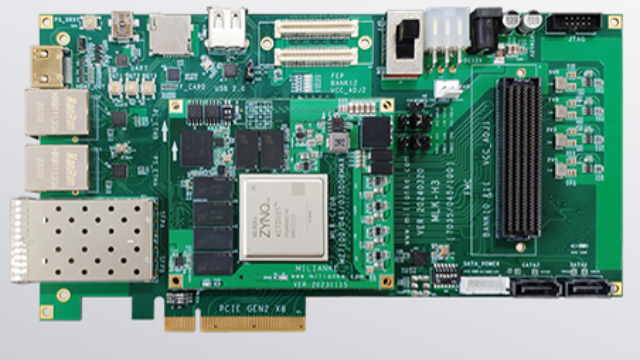

米联客MIZ702NFPGA开发板(Zynq-7020款)米联客MIZ702N开发板基于XilinxZynq-7020芯片设计,聚焦嵌入式系统入门与轻量型应用开发。该芯片集成双核ARMCortex-A9处理器与28nmFPGA逻辑资源(28万逻辑单元),兼顾软件控制与硬件加速能力。硬件配置上,开发板搭载512MBDDR3内存、16GBeMMC闪存,板载HDMI输出接口、USBOTG接口、千兆以太网接口及40针扩展接口,可连接摄像头、显示屏等外设,搭建完整嵌入式应用场景。软件支持方面,开发板适配Vitis开发环境与Petalinux操作系统,提供基础Linux镜像与驱动源码,用户可快速实现“处理器+FPGA”协同开发。配套资料包含多个入门案例,如HDMI图像显示、以太网数据传输、GPIO控制等,每个案例附带详细步骤说明与代码注释。该开发板尺寸为12cm×10cm,采用沉金工艺提升接口耐用性,适合嵌入式爱好者入门实践,也可作为高校嵌入式课程的教学实验平台,帮助用户掌握软硬件协同设计思路。 FPGA 开发板逻辑资源使用率实时可查。

,需依赖外部配置存储器实现上电自动加载设计文件。开发板常用的配置存储器包括SPIFlash、ParallelFlash和SD卡,其中SPIFlash因体积小、功耗低、成本适中成为主流选择,容量通常从8MB到128MB不等,可存储多个FPGA配置文件,支持通过板载按键切换加载不同设计。ParallelFlash则具备更快的读取速度,适合对配置时间要求严格的场景,但占用PCB空间更大。部分开发板还支持通过JTAG接口直接从计算机加载配置文件,无需依赖外部存储器,这种方式在开发调试阶段尤为便捷,开发者可快速烧录修改后的代码,验证逻辑功能,而无需频繁插拔存储设备。 FPGA 开发板接口防反插设计保护硬件安全。学习FPGA开发板语法

FPGA 开发板是否支持多电压域外设接入?江苏ZYNQFPGA开发板学习板

1.FPGA开发板的时钟模块作用时钟信号是FPGA数字逻辑设计的“脉搏”,开发板上的时钟模块通常由晶体振荡器、时钟缓冲器和时钟分配网络组成。晶体振荡器能提供高精度的固定频率信号,常见频率有25MHz、50MHz、100MHz等,部分板卡还会集成可配置的时钟发生器,支持通过软件调整输出频率,满足不同算法对时钟周期的需求。时钟缓冲器可将单一时钟信号复制为多路同步信号,分配给FPGA内部的不同逻辑模块,避免因信号延迟导致的时序偏差。在高速数据处理场景中,如图像处理或通信信号解调,时钟模块的稳定性直接影响数据采样精度和逻辑运算的同步性,因此部分开发板还会加入时钟抖动抑制电路,进一步降低信号噪声。江苏ZYNQFPGA开发板学习板