FPGA开发板是数字电路教学的重要工具,能将抽象的逻辑概念转化为直观的硬件实验。在基础教学中,学生可通过编写简单的Verilog代码,实现与门、或门、触发器等基本逻辑单元,并通过板载LED或数码管观察输出结果,理解数字信号的传输与运算规律。进阶实验中,可基于开发板设计计数器、定时器、状态机等复杂逻辑模块,结合按键输入实现交互功能,例如设计一个带启停控制的秒表。部分开发板还配套有教学实验手册和代码示例,涵盖从基础逻辑到综合系统的完整案例,帮助学生逐步掌握硬件描述语言和FPGA设计流程。与传统实验箱相比,FPGA开发板的灵活性更强,支持学生自主设计和修改电路功能,培养创新思维和实践能力。 FPGA 开发板外设驱动代码简化应用开发。黑龙江工控板FPGA开发板特点与应用

FPGA开发板在教育教学中具有重要的价值。对于高校电子信息类的学生而言,开发板是将理论知识转化为实践能力的重要媒介。在数字电路课程学习中,学生通过在开发板上实现简单的逻辑电路,如计数器、译码器等,直观地理解数字电路的工作原理与设计方法。在学习硬件描述语言时,学生利用开发板进行实际项目练习,从简单的LED闪烁到复杂的数码管动态显示,逐步掌握Verilog或VHDL语言的编程技巧。在综合性课程设计与毕业设计中,开发板更是学生展示创新能力的平台。学生可以基于开发板开展如智能小车设计、简易数字示波器制作等项目,综合运用多门课程所学知识,锻炼系统设计、调试与优化的能力,培养学生的工程实践素养与创新思维,为未来从事电子信息相关行业的工作奠定坚实的基础。河南学习FPGA开发板工业模板FPGA 开发板外设接口过压保护保障安全。

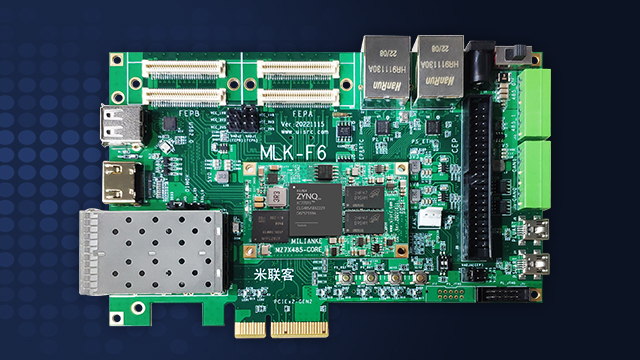

米联客MIZ702NFPGA开发板(Zynq-7020款)米联客MIZ702N开发板基于XilinxZynq-7020芯片设计,聚焦嵌入式系统入门与轻量型应用开发。该芯片集成双核ARMCortex-A9处理器与28nmFPGA逻辑资源(28万逻辑单元),兼顾软件控制与硬件加速能力。硬件配置上,开发板搭载512MBDDR3内存、16GBeMMC闪存,板载HDMI输出接口、USBOTG接口、千兆以太网接口及40针扩展接口,可连接摄像头、显示屏等外设,搭建完整嵌入式应用场景。软件支持方面,开发板适配Vitis开发环境与Petalinux操作系统,提供基础Linux镜像与驱动源码,用户可快速实现“处理器+FPGA”协同开发。配套资料包含多个入门案例,如HDMI图像显示、以太网数据传输、GPIO控制等,每个案例附带详细步骤说明与代码注释。该开发板尺寸为12cm×10cm,采用沉金工艺提升接口耐用性,适合嵌入式爱好者入门实践,也可作为高校嵌入式课程的教学实验平台,帮助用户掌握软硬件协同设计思路。

FPGA开发板在教育领域发挥着重要作用,是培养电子信息类专业人才的得力助手。对于高校相关专业的学生而言,开发板是学习数字电路、硬件描述语言、数字系统设计等课程的理想实践平台。在数字电路课程中,学生可以通过在FPGA开发板上搭建简单的逻辑电路,如与门、或门、触发器等,直观地理解数字电路的基本原理和工作方式。在学习硬件描述语言时,学生利用Verilog或VHDL语言在开发板上实现各种数字系统,如计数器、寄存器、加法器等,将抽象的语言知识转化为实际的硬件电路,加深对语言的理解和掌握。在数字系统设计课程中,学生基于开发板进行综合性的项目实践,如设计一个简单的微处理器系统,从指令集设计、数据通路搭建到控制器实现,锻炼学生的系统设计能力和创新思维。同时,开发板还可用于学生参加各类电子设计竞赛,激发学生的学习兴趣和创新热情,培养学生的团队协作能力和解决实际问题的能力,为学生未来从事电子信息领域的工作或继续深造奠定坚实的实践基础。FPGA 开发板接口间距符合标准封装尺寸。

FPGA开发板在物联网领域的应用日益。在智能家居系统搭建中,开发板可作为枢纽连接各类智能设备。通过Wi-Fi或蓝牙模块,开发板与智能手机等终端设备建立通信,接收用户的控制指令;同时,利用GPIO接口连接各类传感器,如温湿度传感器、人体红外传感器等,实时采集家居环境数据。基于采集到的数据,开发者可以在FPGA上编写逻辑程序,实现自动化的家居控制场景。例如,当检测到室内温度过高时,自动开启空调;检测到有人进入房间,自动打开灯光。此外,开发板还可以通过以太网接口接入家庭网关,与云端服务器进行数据交互,实现远程监控与控制功能。用户即便不在家中,也能通过手机APP查看家中设备状态,并进行远程操作,为用户打造便捷、智能的家居生活体验。FPGA 开发板按键可作为输入控制信号源。河南学习FPGA开发板工业模板

FPGA 开发板网络接口支持远程调试。黑龙江工控板FPGA开发板特点与应用

FPGA开发板的信号完整性是指信号在传输过程中保持原有特性的能力,直接影响系统的稳定性和性能,尤其在高速接口(如PCIe、DDR、HDMI)设计中至关重要。信号完整性优化需从PCB设计、元器件选型和时序约束三个方面入手。PCB设计中,需控制传输线阻抗匹配(如50Ω、100Ω差分),避免阻抗突变导致信号反射;采用差分信号传输,减少电磁干扰(EMI);优化布线拓扑,缩短信号路径,减少串扰。元器件选型中,需选用高速率、低抖动的晶体振荡器和时钟缓冲器,确保时钟信号稳定;选用低寄生参数的连接器和电容电阻,减少信号衰减。时序约束中,需在开发工具中设置合理的时钟周期、建立时间和保持时间,确保数据在正确的时序窗口内传输;通过时序分析工具检查时序违规,调整逻辑布局和布线,实现时序收敛。信号完整性问题常表现为数据传输错误、图像失真、接口不稳定,可通过示波器观察信号波形,分析反射、串扰、抖动等问题,针对性优化设计。 黑龙江工控板FPGA开发板特点与应用